# USER'S REFERENCE MANUAL

P8-16

16 Bit Bus Access Adapter for PROTO-8

Model No.

100-7578

Doc. No.

M7578

Rev: 1.1

06/22/06

© Copyright 1998 - 2006 SCIDYNE "All Rights Reserved"

Previous revision: 1.0 3/11/98

This document DISCLAIMER: contains proprietary information regarding SCIDYNE and its products. The information is subject to change without notice. SCIDYNE makes no warranty of any kind with regard to this material, including but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SCIDYNE shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material. No part of this document may be duplicated in any form without prior written consent of SCIDYNE.

WARRANTY: SCIDYNE warrants this product against defects in materials and workmanship and, that it shall conform to specifications current at the time of shipment, for a period of one year from date of shipment. Duration and conditions of warranty may be superseded when the product is integrated into other SCIDYNE products. During the warranty period, SCIDYNE will, at its option and without charge to Buyer, either repair or replace products which prove defective. Repair or replacement of a defective product or part thereof does not extend the original warranty period.

WARRANTY SERVICE: For warranty service or repair, this product must be returned to a service facility designated by SCIDYNE. The Buyer must obtain prior approval and a Return Material Authorization (RMA) number before returning any products. The RMA number must be clearly visible on the shipping container. The Buyer shall prepay shipping and insurance charges to the service facility and SCIDYNE shall pay shipping and insurance charges to Buyer's facility for products repaired or SCIDYNE may, at its replaced. discretion, bill the Buyer for return shipping and insurance charges for products received for repair but determined to be non-defective. Additionally, the Buyer shall pay all shipping charges, duties and taxes for products returned to SCIDYNE from another country.

#### LIMITATION OF WARRANTY

The forgoing warranty shall not apply to defects resulting from improper or negligent maintenance by the Buyer, Buyer-supplied products or interfacing, unauthorized modifications or misuse, operation outside the published specifications of the product or improper installation site preparation or maintenance, or the result of an accident. The design and implementation of any circuit using this product is the sole responsibility of the Buyer. SCIDYNE does not warrant the Buyer's circuitry or malfunctions of SCIDYNE products that result from the Buyer's circuitry. In addition, SCIDYNE does not warrant any damage that occurs as a result of the Buyer's circuit or any defects that result from Buyer-supplied products. Warranty does not cover normal preventative maintenance items such as fuse replacement, lamp replacement, resetting of circuit breakers, cleaning of the Product or problems caused by lack of preventative maintenance, improper cleaning, improper programming or improper operating procedures. No other warranty is expressed or implied. SCIDYNE specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. Some states do not permit limitation or exclusion of implied warranties; therefore, the aforesaid limitation(s) or exclusion(s) may not apply to the Buyer. This warranty gives you specific legal rights and you may have other rights which vary from state to state.

#### CERTIFICATION

Testing and other quality control techniques are utilized to the extent SCIDYNE deems necessary to support this warranty. Specific testing of all parameters is not necessarily performed, except those mandated by government requirements.

#### 30-DAY PRODUCT EVALUATION

POLICY: SCIDYNE offers a no-risk trial for initial, low quantity, evaluation purchases. Items purchased for evaluation can be returned within 30 days for a full refund less shipping charges. The Buyer must obtain a Return Material Authorization (RMA) number before returning any products. The entire package, including hardware, software, documentation, discount coupons and any other accessories supplied must be returned intact and in new and working condition. This policy

will not be honored for packages that are not returned complete and intact. The Buyer shall prepay shipping and insurance charges to SCIDYNE. To expedite the return process, the RMA number must be clearly visible on the shipping container. SCIDYNE will cancel the invoice, refund by check or issue credit to your credit card within 10 days after receipt of returned merchandise.

#### LIFE SUPPORT POLICY

Certain applications may involve the risks of death, personal injury or severe property or environmental damage ("Critical Applications").

SCIDYNE products are not designed, intended, authorized or warranted to be suitable for use in life-support applications, devices or systems or other critical applications without the express written approval of the president of SCIDYNE.

### SAFETY AND USAGE CONVENTIONS

NOTE: Contains important information and useful tips that will assist in the understanding and operation of the product.

CAUTION: Calls attention to a procedure, practice or condition that could possibly cause personal injury or damage to equipment.

⚠ WARNING: Calls attention to a procedure, practice or condition that could possibly cause severe bodily injury, death or extensive equipment damage.

### Introduction

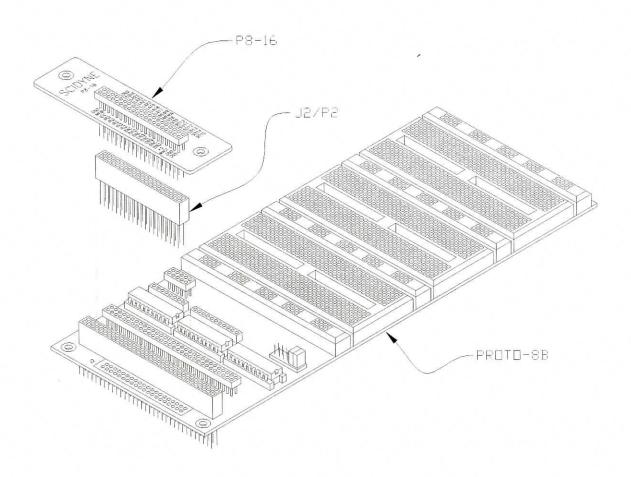

The P8-16 is a companion product for use with our PROTO-8 PC/104 prototyping breadboard. The adapter provides simple and cost effective means to upgrade a standard PROTO-8 for use in 16 bit projects. This allows a user to rapidly evaluate and develop more advanced PC/104 designs. The P8-16 simply plugs into the J2/P2 connector located on the PROTO-8. All J2/P2 signals are routed to a socket strip which directly accepts 20-28AWG solid wire or component leads. Each signal is clearly identified, reducing the chances of wiring errors and making connections straight forward. All the original functionality of the PROTO-8 is maintained while at the same time providing a clear path to 16 bit hardware development. The P8-16 may be freely unplugged and re-installed as the user switches between 8 and 16 bit projects.

MOTE: The J2/P2 connector is not installed on a stock PROTO-8. This connector is required to use the P8-16 and must be purchased separately. Order part number 104-0002.

## Signal Descriptions

NOTE: An in depth explanation for each signal's purpose and its use is beyond the scope of this manual. Many excellent books exist which fully describe the operation of the PC/104 and ISA bus architecture. The reader is encouraged to seek one of these for a definitive reference.

| PC/104 J2/P2 Signal Descriptions (Listed Alphabetically) |     |                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name                                              | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                 |

| DACKx*                                                   | 0   | <b>DMA Acknowledge</b> These lines are used to acknowledge DMA requests (DRQ5 - DRQ7) and to refresh system dynamic memory (DACK0). They are active low. (DACK1* - DACK3* are located on the J1/P1 connector.)                                                                                                                                                                                              |

| DRQx                                                     | I   | <u>DMA Request</u> These lines are asynchronous channel requests used by peripheral devices to gain DMA service. They are prioritized with DRQ7 being the lowest and DRQ1 being the highest. A request is generated by bringing a DRQ line to an active level (high). The DRQ line must be held high until the corresponding DACK line goes active (low). (DRQ1 - DRQ3 are located on the J1/P1 connector.) |

| IOCS16*                                                  | I   | <u>Input/Output Chip Select 16</u> Used by an I/O device to indicate that it supports 16 bit accesses.  This signal is ignored during memory access cycles.                                                                                                                                                                                                                                                 |

| IRQx                                                     | 1   | Interrupt Request attention. Lower IRQ numbers have higher priority. An Interrupt Request is generated by raisin an IRQ line (low to high) and holding it high until it is acknowledged by the processor (interrupt service routine).                                                                                                                                                                       |

| LA17 - LA23                                              | О   | <u>Latchable Address</u> These system address lines must be latched on the falling edge of BAL if they are required for the entire bus access cycle.                                                                                                                                                                                                                                                        |

| MASTER*                                                  | I   | Master (16 Bit) Used by bus masters to indicate 16 bit data size.                                                                                                                                                                                                                                                                                                                                           |

| MEMCS16*                                                 | 0   | Memory Chip Select 16 Used by a memory resource to indicate that it supports 16 b accesses. This signal is ignored by refresh and DMA controllers during I/O cycles.                                                                                                                                                                                                                                        |

| MEMR* MEMW*                                              | 0   | Memory Read bus. It performs the same function as SMEMR* except that MEMR* can signal a read operation beyond the first one megabyte of system memory. It may be driven by the processor or the DM controller. This signal is active low.                                                                                                                                                                   |

|                                                          |     | Memory Write This command line instructs the memory device to store the data present of the data bus. It performs the same function as SMEMW* except that MEMW* can signal a write operation beyond the first one megabyte of system memory. It may be driven by the processor or the DMA controller. This signal is active low.                                                                            |

| SBHE*                                                    | 0   | System Byte High Enable Driven by the bus master to indicate that valid data resides on the upper data lines SD8 - SD15. When active, this signal can be qualified with SA0 to determine if data is 8 bits (SA0=1) or 16 bits (SA0=0) in size.                                                                                                                                                              |

| SD8 - SD15                                               | I/O | System Data Bus SD0 - SD7 are located on the J1/P1 connector. SD0 is the least significate bit and SD15 is the most significant bit. The platform byte swapper circuitry assure that SD SD15 are valid whenever SBHE* is active.                                                                                                                                                                            |