# USER'S REFERENCE MANUAL

# DIO24 24 Bit Digital I/O Module for PC/104

Model No. Doc. No.

100-7543 M7543

Rev: 1.5 6/14/06

649 School Street / Pembroke, MA 02359 USA / Tel: (781) 293-3059 *www.scidyne.com*  © Copyright 1997 - 2006 SCIDYNE "All Rights Reserved" Previous revision: 1.4 1/28/05

**DISCLAIMER:** This document contains proprietary information regarding SCIDYNE and its products. The information is subject to change without notice. SCIDYNE makes no warranty of any kind with regard to this material, including but not limited to, the implied warranties of merchantability and fitness for a particular purpose. SCIDYNE shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this material. No part of this document may be duplicated in any form without prior written consent of SCIDYNE.

WARRANTY: SCIDYNE warrants this product against defects in materials and workmanship and, that it shall conform to specifications current at the time of shipment, for a period of one year from date of shipment. Duration and conditions of warranty may be superseded when the product is integrated into other SCIDYNE products. During the warranty period, SCIDYNE will, at its option and without charge to Buyer, either repair or replace products which prove defective. Repair or replacement of a defective product or part thereof does not extend the original warranty period.

WARRANTY SERVICE: For warranty service or repair, this product must be returned to a service facility designated by SCIDYNE. The Buyer must obtain prior approval and a Return Material Authorization (RMA) number before returning any products. The RMA number must be clearly visible on the shipping container. The Buyer shall prepay shipping and insurance charges to the service facility and SCIDYNE shall pay shipping and insurance charges to Buyer's facility for products repaired or replaced. SCIDYNE may, at its discretion, bill the Buyer for return shipping and insurance charges for products received for repair but determined to be non-defective. Additionally, the Buyer shall pay all shipping charges, duties and taxes for products returned to SCIDYNE from another country.

### **LIMITATION OF WARRANTY:**

The forgoing warranty shall not apply to defects resulting from improper or negligent maintenance by the Buyer, Buyer-supplied products or interfacing, unauthorized modifications or misuse, operation outside the published specifications of the product or improper installation site preparation or maintenance, or the result of an accident. The design and implementation of any circuit using this product is the sole responsibility of the Buyer. SCIDYNE does not warrant the Buyer's circuitry or malfunctions of SCIDYNE products that result from the Buyer's circuitry. In addition, SCIDYNE does not warrant any damage that occurs as a result of the Buyer's circuit or any defects that result from Buyersupplied products. This Warranty does not cover normal preventative maintenance items such as fuse replacement, lamp replacement, resetting of circuit breakers, cleaning of the Product or problems caused by lack of preventative maintenance, improper cleaning, improper programming or improper operating procedures. No other warranty is expressed or implied. SCIDYNE specifically disclaims the implied warranties of merchantability and fitness for a particular purpose. Some states do not permit limitation or exclusion of implied warranties; therefore, the aforesaid limitation(s) or exclusion(s) may not apply to the Buyer. This warranty gives you specific legal rights and you may have other rights which vary from state to state.

**CERTIFICATION:** Testing and other quality control techniques are utilized to the extent SCIDYNE deems necessary to support this warranty. Specific testing of all parameters is not necessarily performed, except those mandated by government requirements.

### <u>30-DAY PRODUCT</u> EVALUATION POLICY:

SCIDYNE offers a no-risk trial for initial, low quantity, evaluation purchases. Items purchased for evaluation can be returned within 30 days for a full refund less shipping charges. The Buyer must obtain a Return Material Authorization (RMA) number before returning any products. The entire package, including hardware, software, documentation, discount coupons and any other accessories supplied must be returned intact and in new and working condition. This policy will not be honored for packages that are not returned complete and intact. The Buyer shall prepay shipping and insurance charges to SCIDYNE. To expedite the return process, the RMA number must be clearly visible on the shipping container. SCIDYNE will cancel the invoice, refund by check or issue credit to your credit card within 10 days after receipt of returned merchandise.

**LIFE SUPPORT POLICY:** Certain applications may involve the risks of death, personal injury or severe property or environmental damage ("Critical Applications").

SCIDYNE products are not designed, intended, authorized or warranted to be suitable for use in life-support applications, devices or systems or other critical applications without the express written approval of the president of SCIDYNE.

# Table of Contents

| INTRODUCTION                        | 1 |

|-------------------------------------|---|

| MODULE SETUP                        | 2 |

| DIO24 Factory Default Configuration | 2 |

| J4 Interrupt Input Channel          |   |

| J5 Interrupt Edge                   |   |

| J6 I/O Base Address                 |   |

| J7 Host Interrupt                   | 3 |

| HARDWARE INTERFACE                  | 4 |

| J3 Connector Pinout                 | 4 |

| I/O stage operation                 | 5 |

| INTERRUPTS                          |   |

| Interrupt Status Register           |   |

| Interrupt Timing Sequence           | 7 |

| SPECIFICATIONS                      | 8 |

# **Conventions and Terminology Used Throughout This Publication**

### **Safety and Usage Conventions**

$\square$  NOTE: Contains important information and useful tips that will assist in the understanding and operation of the product.

CAUTION: Calls attention to a procedure, practice or condition that could possibly cause personal injury or damage to equipment.

<sup>(1)</sup> WARNING: Calls attention to a procedure, practice or condition that could possibly cause severe bodily injury, death or extensive equipment damage.

### **Terminology**

Host This is the computer or similar device into which the DIO24 is plugged.

**Logic conditions** Unless otherwise noted, logic signals are designated as TRUE (Set) and FALSE (Clear). Names with an asterisk (\*) postscript are inverted or active low. Unless otherwise noted TRUE is considered logic "1" (+5vdc) and FALSE is logic "0" (0vdc).

<u>Numbering Systems</u> Computerized equipment often requires its numeric data to be represented in different forms depending on the audience and information being conveyed. Decimal numbers are typically used for end-user data entry and display while internally these values are converted and manipulated in native binary. Hexadecimal numbers are often used by programmers as an intermediate level between binary and decimal notations.

| Base | Name        | Format (MS <> LS)        |

|------|-------------|--------------------------|

| 2    | Binary      | 1011 1001                |

| 10   | Decimal     | 185                      |

| 16   | Hexadecimal | 0xB9 or B9 <sub>16</sub> |

### **Multi-Byte Word Formats**

Unless otherwise specified numbers or registers spanning multiple bytes are stored in "little endian" format. The first address (ADDR+0) will contain the Least Significant Byte (LSB) while the Most Significant Byte (MSB) will reside at the highest address.

| ADDR+0 | ADDR     | ADDR+n |

|--------|----------|--------|

| LSB    | LS <> MS | MSB    |

# **INTRODUCTION**

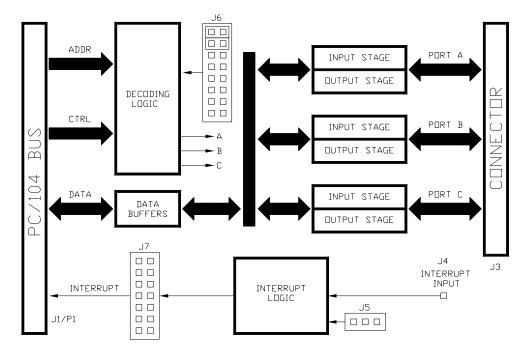

The DIO24 is a 24 bit (channel), non-isolated, digital input/output module specifically designed to provide the high current drive capability required by many peripheral components. It physically conforms to the PC/104 form factor. The 24 channels are grouped across three 8 bit ports as shown in the block diagram below. Unlike competitive products which use a common 8255 chip, each output of the DIO24 can passively source 2.5ma and actively sink 85ma, sufficient sink current to reliably drive solid state and mechanical relays. Each channel may be individually configured as ether an input or output under software control. This feature eases system design by eliminating the necessity to commit an entire port as being used strictly for input or output operations. The lack of a direction register also prevents the problem of all channels resorting back to high impedance inputs during configuration changes or transients caused by inductive loads. Any single input channel can also be used to interrupt the host when that channel changes state. A unique level-edge interrupt detection circuit assures even short duration pulses are recognized. The use of CMOS circuitry provides low power consumption as well as high noise immunity. External peripheral components attach to the DIO24 by means of a 50 conductor IDC type connector. The pinout of this connector is fully compatible with industry standard solid state relay racks.

Figure 1 – DIO24 Block Diagram

# **MODULE SETUP**

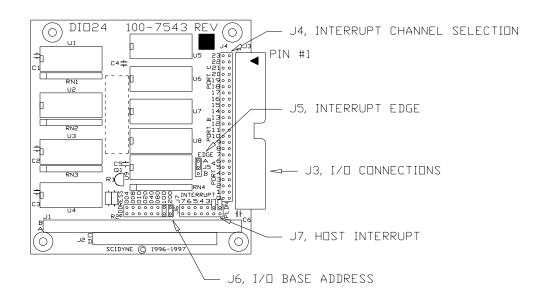

Before the DIO24 can be put into service it must be properly configured for the desired operating modes. This is accomplished by placing shorting jumpers at various locations on the module. The component identification is shown in figure 2. Each DIO24 comes from the factory set to a basic functional default configuration. The user is free to change the default settings to satisfy any particular application requirements. A full explanation for each of the jumper settings appears on subsequent pages.

| DIO24 Factory Default Configuration |                                   |                                         |  |  |  |  |

|-------------------------------------|-----------------------------------|-----------------------------------------|--|--|--|--|

| Jumper Block                        | Function                          | Default Setting                         |  |  |  |  |

| J4                                  | Interrupt Input Channel Selection | None, No wire jumper installed          |  |  |  |  |

| J5                                  | Interrupt Edge                    | J5-A Installed                          |  |  |  |  |

| J6                                  | I/O Base Address                  | 0x300, J6-100 and J6-200 Installed      |  |  |  |  |

| J7                                  | Host Interrupt                    | Disabled, No shorting jumpers installed |  |  |  |  |

Figure 2 - DIO24 Component Identification

# J4 Interrupt Input Channel

The input channel to be used for interrupts is set by soldering a single wire jumper across the appropriate pair of J4 holes. The channel identification numbers (0-23) are clearly printed on the circuit board. If frequent changes to the assignment of the interrupt input channel are anticipated a 24 pin by 2 row jumper block and shorting jumper can be installed instead.

CAUTION: When installing the wire jumper be sure to use solid wire in the range of 20-24AWG. Follow proper soldering techniques, use only "electronic grade" solder, trim the connections and remove any flux residue remaining on the board.

SCIDYNE can perform this modification for you when the DIO24 is purchased in production quantities. Contact the SCIDYNE sales department for further details.

# J5 Interrupt Edge

The polarity of the input signal which will cause an interrupt is selected by this jumper block. A jumper installed on position J5-A will cause an interrupt when the input changes state from normally high to low. A jumper installed at J5-B will cause an interrupt when the input changes from normally low to high. Some devices, such as solid-state relays, cause an inversion of the signal presented to the DIO24. This in turn transposes the function of jumpers J5-A and J5-B in relation to actual field wiring.

# J6 I/O Base Address

The DIO24 occupies four consecutive bytes in the hosts I/O map. The default address of 0x300 can be changed to any four byte boundary in the range of 0x000 to 0x3fc (0 to 1020<sub>10</sub>). Each position of J6 corresponds to a specific "weighted" address value. The I/O base address is calculated by adding together the "weighted" value for each installed jumper. For example, the factory default address of 0x300 is set by placing shorting jumpers at the 100 and 200 positions while all other locations are left open. The values printed on the circuit board are in hexadecimal notation.

🖉 NOTE: Addresses between 0x000 through 0x0ff are generally used by the host and should be avoided. *Make sure the I/O address selected will not conflict with any existing I/O hardware.*

# J7 Host Interrupt

Jumper block J7 configures which host interrupt will be associated with the DIO24. The choices are IRQ 9(2), 3, 4, 5, 6 or 7. Interrupt capability is disabled by leaving all positions of jumper block J7 open. The interrupt driver on the DIO24 conforms to the method for interrupt sharing as outlined in the PC/104 specification. This method recommends that one of the PC/104 modules sharing an IRQ provide a passive pull-down resistor to ground. The DIO24 can supply the pull-down resistor when a shorting jumper is installed at the PLDN position of J7.

MOTE: Try selecting an interrupt which is not currently being used by other system resources. If interrupts must be shared make sure all the software applications involved supports interrupt sharing. To prevent excessive current draw and the possibility of erroneous operation, use only one pull-down per IRQ. IRQ9 is re-directed to IRO2 on most AT style computers.

# HARDWARE INTERFACE

External devices attach to the DIO24 through J3, a 50 pin IDC type connector. The pinout for J3 is shown below. It is compatible with 8, 16 and 24 position solid state relay racks offered by various manufactures. The DIO24 is also intended to be used to interface switch contacts, relays, LEDs and any other common peripheral devices. A companion terminal board (PN 100-7625/50) is available to make field wiring to these components easier.

| J3 Connector Pinout |                      |      |           |             |                  |             |  |

|---------------------|----------------------|------|-----------|-------------|------------------|-------------|--|

| PORT A              |                      | PORT | ΓВ        | PORT C      |                  |             |  |

| Bit                 | Bit Base address + 0 |      | Base addr | ess + 1     | Base address + 2 |             |  |

|                     | I/O<br>Channel       |      |           | J3<br>Pin # | I/O<br>Channel   | J3<br>Pin # |  |

| 0                   | CH-0                 | 47   | CH-8      | 31          | CH-16            | 15          |  |

| 1                   | CH-1                 | 45   | СН-9      | 29          | CH-17            | 13          |  |

| 2                   | CH-2                 | 43   | CH-10     | 27          | CH-18            | 11          |  |

| 3                   | СН-3                 | 41   | CH-11     | 25          | CH-19            | 9           |  |

| 4                   | CH-4                 | 39   | CH-12     | 23          | CH-20            | 7           |  |

| 5                   | СН-5                 | 37   | CH-13     | 21          | CH-21            | 5           |  |

| 6                   | СН-6                 | 35   | CH-14     | 19          | СН-22            | 3           |  |

| 7                   | CH-7                 | 33   | CH-15     | 17          | CH-23            | 1           |  |

Special Notes:

J3-2 through J3-50 (even pins) are connected to common

J3-49 is +5vdc unfused supplied by host

# I/O stage operation

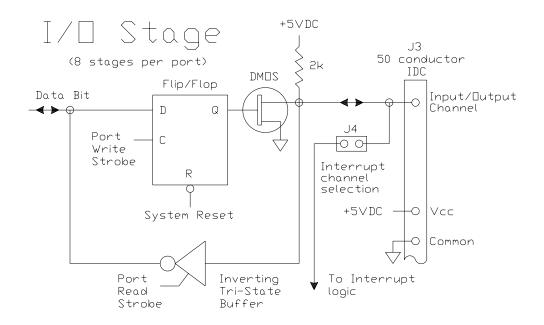

Upon system reset the flip/flop's output is cleared deactivating the DMOS transistor and placing it in a high impedance state. The I/O channel is pulled high by virtue of the 2k ohm resistor. Its value has been chosen to supply reasonable source current while the I/O stage functions as an output, yet be capable of being overridden by external devices when used as an input. The level of the I/O channel is presented to the input of the inverting tri-state buffer. Performing an I/O read operation on the corresponding port activates the tri-state buffer and passes the inverted state of the I/O channel to the host computer. As shown, the host computer would read a logic 0 for this bit of the port. If an external device were to pull the I/O channel to common, the computer would then read a logic 1. The users software can perform an invert operation if the actual state of the I/O channel must be represented.

When the I/O stage functions as an output, the 2k pull-up resistor supplies up to 2.5ma of source current to external devices. Performing an I/O write operation to the port with the corresponding I/O channel bit at logic 1 sets the flip/flop which activates the DMOS transistor. The transistor pulls the I/O channel hard to common and provides a low impedance path capable of sinking 85ma. An I/O read operation on this bit essentially returns the logic state stored in the flip/flop due to the double inversion provided by the transistor and buffer. This feature is extremely useful when performing read-modify-write bit manipulations in software on a single channel.

Figure 3 – I/O Stage Circuitry

# **INTERRUPTS**

The DIO24 allows any single channel used as an input to optionally interrupt the host when that channel changes to a predetermined state. Interrupts are detected using a unique Level-Edge circuit. This feature allows external signals to interrupt the host while that signals remains in a predetermined state. It also captures narrow state change transitions which could otherwise be missed using level type interrupts alone. The polarity of the interrupt as well as which host interrupt will be used can be set to suit the users needs. Refer to the module setup section of this manual for further details.

# Interrupt Status Register

The Interrupt Status Register is used to monitor interrupts generated by the DIO24. It is also used to clear an interrupt request after it has been serviced by writing any single byte value to it. The IS bit is automatically cleared whenever a system hardware reset occurs.

Interrupt Status Register

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |                  |

|----|----|----|----|----|----|----|----|------------------|

| U  | U  | U  | U  | U  | U  | U  | IS | Base Address + 3 |

| -  | -  | -  | -  | -  | -  | -  | 0  | Reset            |

U <u>Undefined</u>

IS Interrupt Status

0 = DIO24 is not requesting interrupt service

1 = DIO24 is requesting interrupt service

# **Interrupt Timing Sequence**

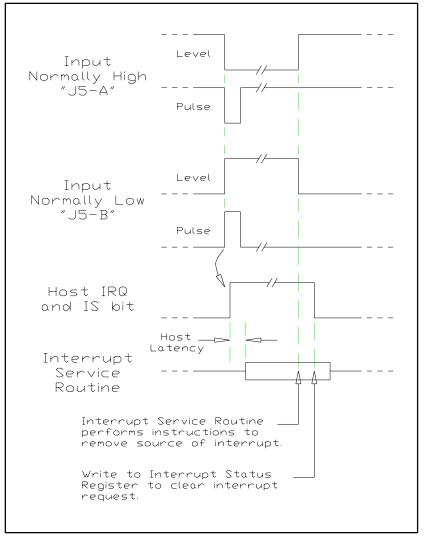

The typical interrupt timing sequence is shown in figure 4. An input normally idles ether high or low as determined by the EDGE setting, jumper block J5. When that input changes state it generates an interrupt request to the host and sets the IS bit in the Interrupt Status Register. If the input signal is actually a momentary pulse the event is stored by the DIO24 Level-Edge The request invokes an circuitry. interrupt service routine on the host. If interrupts are shared, the IS bit can be examined to determine if the DIO24 has caused the request. During the interrupt service routine the input is returned to its idle state by removing the source of the interrupt. This is followed by writing to the Interrupt Status Register which clears the IS bit and releases the interrupt request.

NOTE: The width of an input pulse must be shorter than the entire duration of the interrupt service otherwise multiple interrupts will occur.

Figure 4 – Interrupt Timing Sequence

# SPECIFICATIONS

Number of channels: 24 Individually programmable digital Input/Output channels, non-isolated.

| Input level:                                                                | Logic 0 = 0.8vdc maximum, -0.6vdc minimum<br>Logic 1 = 2.0vdc minimum, 5.6vdc maximum      |                                                                                 |                                                                                                                                                                                                                                                                                                          |                                                              |  |  |  |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--|--|--|

| Output level:                                                               | 0                                                                                          | Logic $0 = \langle 0.4vdc (15ma load)$<br>Logic $1 = \rangle 2.0vdc (1ma load)$ |                                                                                                                                                                                                                                                                                                          |                                                              |  |  |  |

| Max output current: Per channel                                             |                                                                                            | Per channel                                                                     | Source:<br>Sink:                                                                                                                                                                                                                                                                                         | 2.5ma<br>85ma                                                |  |  |  |

| Addressing:                                                                 | 4 con                                                                                      | secutive I/O by                                                                 | tes Jumper se                                                                                                                                                                                                                                                                                            | lectable between 0 and 1020 decimal (0 to 0x3fc hexadecimal) |  |  |  |

| Interrupt:                                                                  | Any single input cha<br>Interrupts:<br>Polarity:<br>Pulse detection:<br>Interrupt sharing: |                                                                                 | annel can be configured to interrupt the host computer when that channel changes state.<br>IRQ 3, 4, 5, 6, 7, 9 (Note: IRQ9 is re-directed as IRQ2 on most AT computers)<br>Selectable positive or negative level-edge<br>2µs pulse width minimum<br>Fully supported including interrupt status register |                                                              |  |  |  |

| <b>Power requirement:</b> +5vdc ±5% @ 20ma typical, external loads excluded |                                                                                            |                                                                                 | l, external loads excluded                                                                                                                                                                                                                                                                               |                                                              |  |  |  |

|                                                                             |                                                                                            |                                                                                 | bliant, 3.6"W x 3.8"L. 8-Bit stack-through.<br>ed for adding J2/P2 connector creating 16-bit stack-through compatibility                                                                                                                                                                                 |                                                              |  |  |  |

| 1 0                                                                         |                                                                                            | nperature: -40°C to 85°C<br>ng relative humidity: 5% to 95%                     |                                                                                                                                                                                                                                                                                                          |                                                              |  |  |  |